### NANOELECTRONIC TECHNOLOGY: In Search of the Ultimate Device Structures

S. M. SZE National Chiao Tung University National Nano Device Laboratories Hsinchu, Taiwan

## OUTLINE

- INTRODUCTION

- EVOLUTION OF MOSFET STRUCTURES

- MAJOR ISSUES OF DEVICE SCALING

- NANOTECHNOLOGY OPTIONS AND ULTIMATE DEVICE

- CONCLUSION

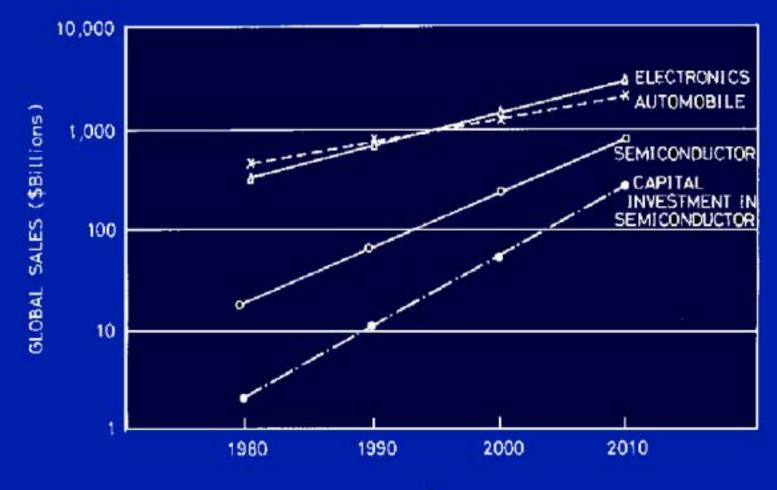

### SEMICONDUCTOR INDUSTRY: A KEY INDUSTRY FOR 21<sup>ST</sup> CENTURY

YEAR

### **PROGRESS IN MICROELECTRONICS**

| Year                             | 1961            | 1970-1971 | 2003               | Ratio                    |

|----------------------------------|-----------------|-----------|--------------------|--------------------------|

| Design Rule (µm)                 | 25              |           | 0.09               | 270 ↓                    |

| V <sub>DD</sub> (V)              | 5               |           | 1.2                | 4 ↓                      |

| Wafer diameter (mm)              | 25              |           | 300                | 12 1                     |

| Devices per chip                 | 6               |           | 8× 10 <sup>9</sup> | 10 <sup>s</sup> 1        |

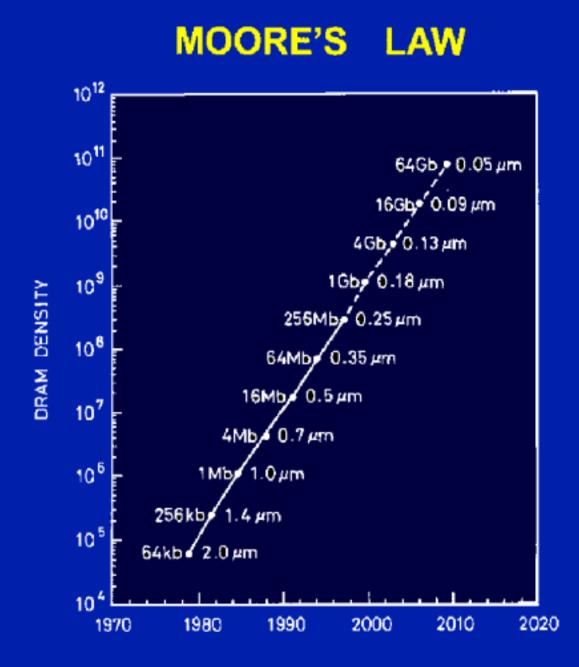

| DRAM density (bit)               | -               | 1k        | 4G                 | 4×10⁵ ↑                  |

| Nonvolatile memory density (bit) | -               | 2k        | 2G                 | <b>10</b> <sup>8</sup> ↑ |

| Microprocessor clock rate (Hz)   | -               | 750k      | 3G                 | 4×10 <sup>4</sup> ↑      |

| Transistor shipped / year        | 10 <sup>7</sup> |           | 10 <sup>18</sup>   | 10 <sup>11</sup> ↑       |

| Average transistor price (\$)    | 10              |           | 2×10 <sup>-7</sup> | 5×10 <sup>7</sup> ↓      |

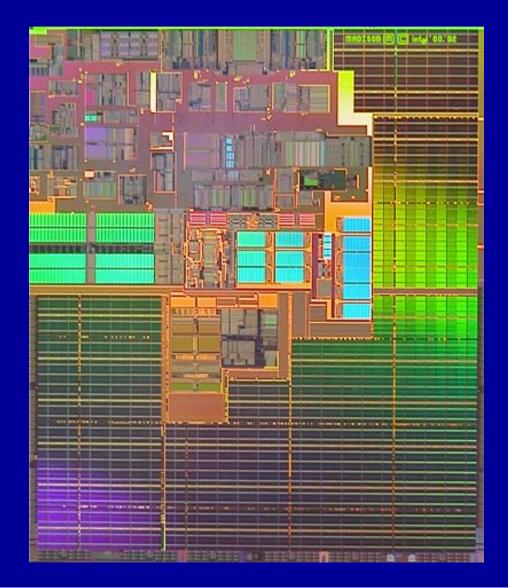

#### ITANIUM MICROPROCESSOR (410 Million Transistors 374 mm<sup>2</sup> 0.13µm 1.5 GHz)

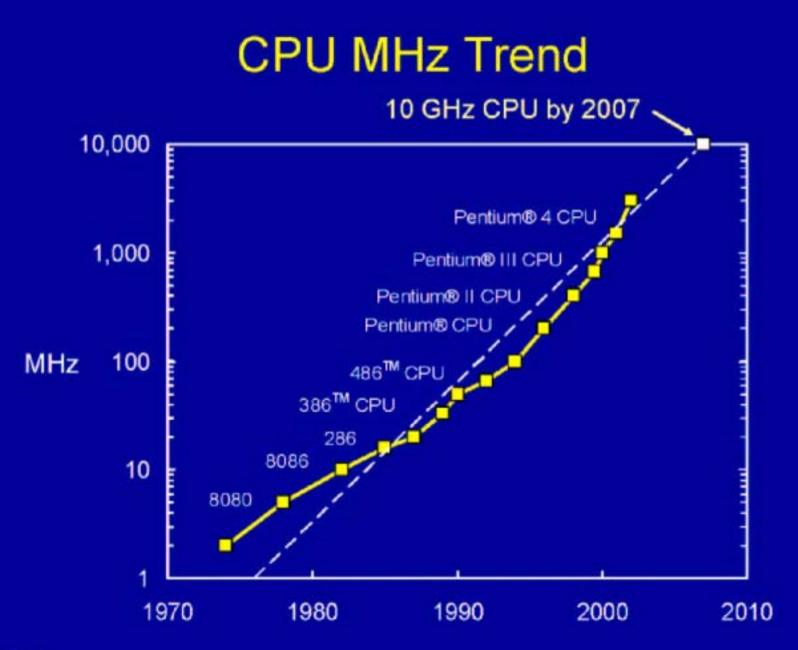

YEAR

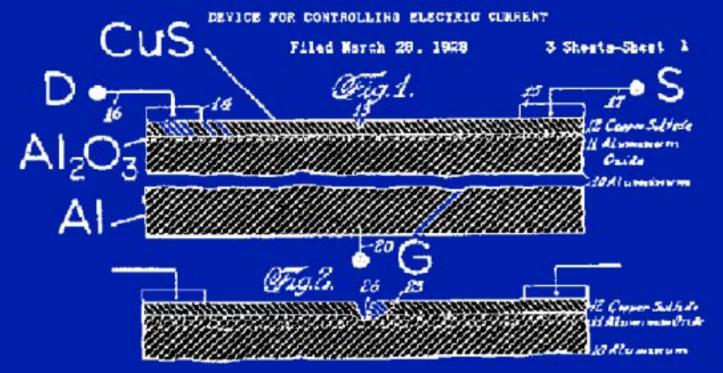

Patented Mar. 7, 1933

1,900,018

#### UNITED STATES PATENT OFFICE

JULIUS ZDOAR IILIKHENLD, OF PROOKLIFF. NEW YORK DEVICE FOR CONTROLLING RELECTRIC CURRENT Application diet March 18, 1800. Sector St. SD,711.

#### MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor)

## FIRST COMMERCIAL MOSFET, 1964 Fairchild Data Sheet for p-Channel MOSFETs

#### PRESIMINARY SPECIFICATIONS -- OCTOBER LIGH #

the second s

PHYSICAL DIMENSIONS

#### FI 100 P-CHANNEL MOS FIELD EFFECT TRANSISTOR DIFFUSED SILICON PLANAR II DEVICE

stand a stand property of the local

The PTGM is a solvers Plankally (page 1:160:3 and Elfen Transmit drags of the others need and experience. At 3 thought of manigues page), the divert for the data indicate window, rate radial sections manifely, and a high OFF to GN encoded region. The BND are to be started with a closer for the started started and the other to be being meet logic laborate takes. The BND are to be started with a former for the started started and the other to be being meet logic laborate takes are personal and started with a laborate to the started started and the takes are started as personal region of the started started started and the started started and the takes are started as personal region of the started started started and the started started started and and excellent DC to high (regardly Backley acrossing).

|                         | WVM ANTINGS (SHEP 2)                                                                                                |                                                                      | The second s |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Have an Tre<br>Borge Te | per Heros                                                                                                           | -010 ta - 100 C<br>-0110 ta - 100 C                                  | 82 11                                                                                                          |

| Tesh Carls              | ar Dipungan dan<br>partak di 1917 Bawa Yunggerdining<br>ul 27 B. Adrianak Tempu natro<br>Inge 4 Gautana             | 10 mm<br>1.3 mm                                                      | The second                                                                                                     |

| Yac<br>Yac<br>Yac       | (Mart al Anoras Managa<br>Gula In Sauras Vanaga (aun 1)<br>Gan La Sauras Vanaga Microsofti (auto 2)<br>Brian Gurren | - No Heche<br>+ Ol Yoshia<br>- Ol Yoshia<br>- Ol Yoshia<br>- 21 oshi | 2                                                                                                              |

NANDLINE INSTRUCTIONS

This is a manifest product device the deferre is a set the data is placed in  $f_{1}$  between the main  $f_{1}$  between the matrix state on the state and an  $f_{1}$  between the matrix  $f_{1}$  and  $g_{2}$  and  $g_{3}$  between the matrix  $f_{2}$  and  $g_{3}$  between the matrix  $f_{3}$  between the matrix  $f_{3}$  and  $g_{3}$  between the matrix  $f_{3}$  and  $g_{3}$  between the matrix  $f_{3}$  and  $g_{3}$  between the matrix  $f_{3}$  between th

Booge All they been smalleds at control with the builty

Trainy. Grade lost end challen prior of everyward of the garger and high circles or net exception. Another a process Head I in some or growth all wellening long type, and

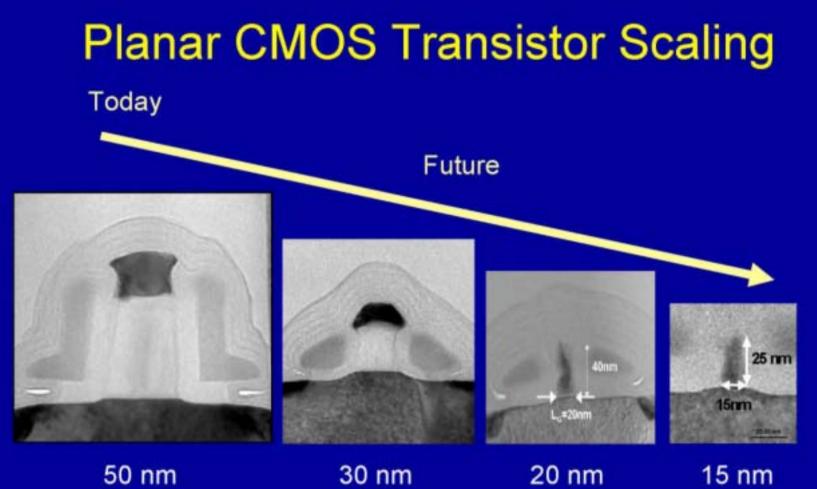

## **Planar CMOS**

Gate Length

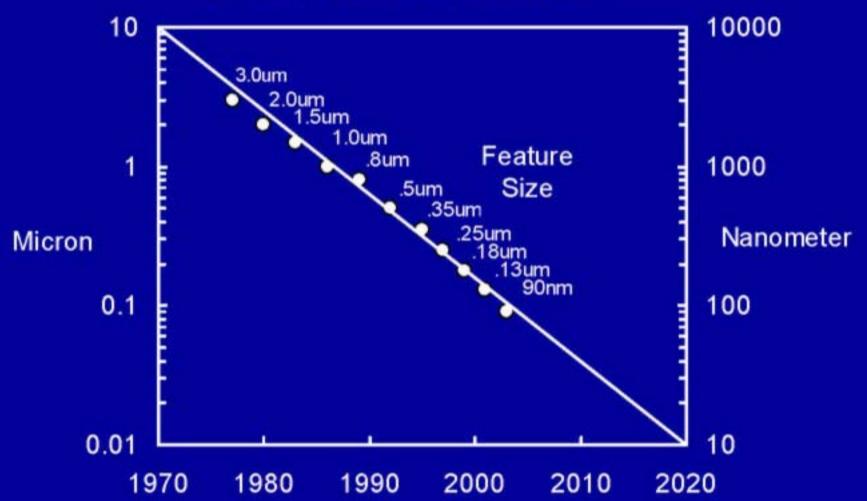

## Feature Size Trend

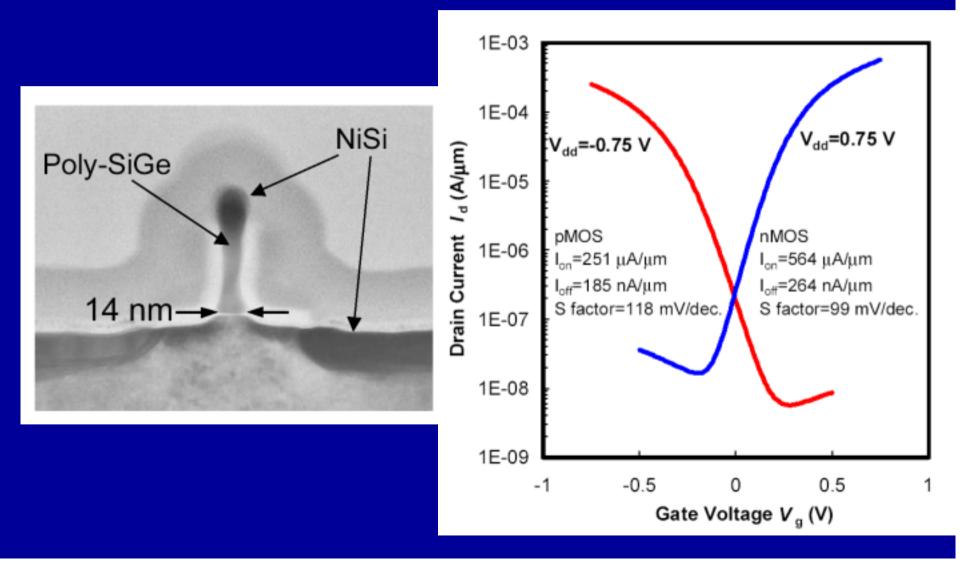

## 14 nm Gate Length CMOS (IEDM'2002, S.27.1, p.639)

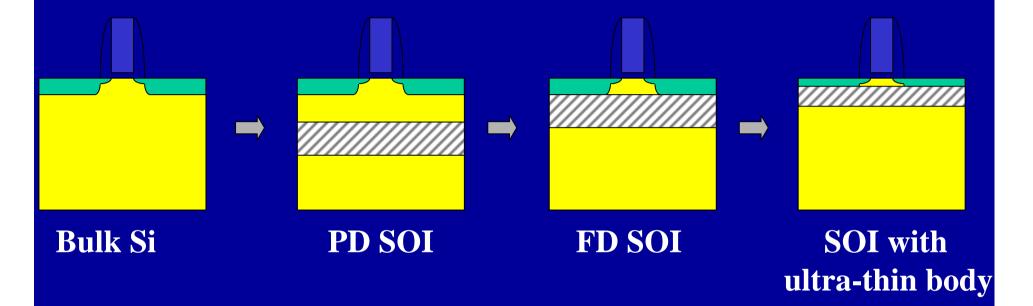

### **Evolution of Device Structure**

#### Targets

- Ideal sub-threshold slope

(~ 60 mV/dec at room temperature)

- High current drive

- Low off current

- Good short-channel effect control

- Non-sensitive to parameter fluctuation

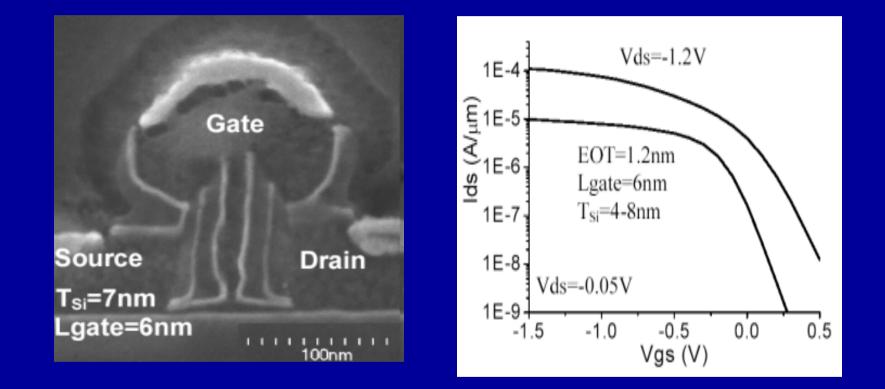

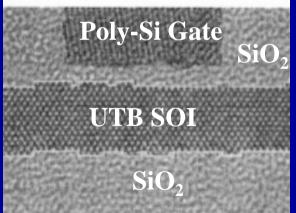

## 6 nm Gate Length UTB SOI PMOS (IEDM'2002, S.10.6, p.267)

## **Issues for UTB SOI CMOS**

• SCE control T<sub>SOI</sub>~1/3L<sub>min</sub>

- Parasitic S/D resistance

- Quantum confinement effect -Vth increase

- Body thickness fluctuation -Vth increase -Mobility degradation

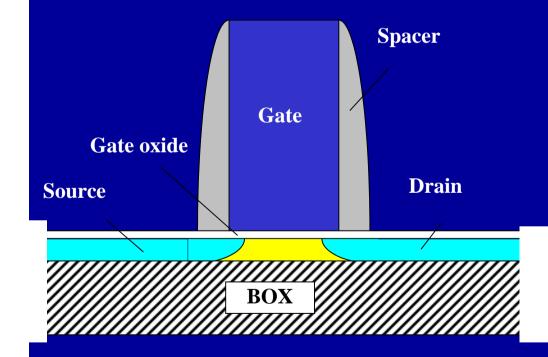

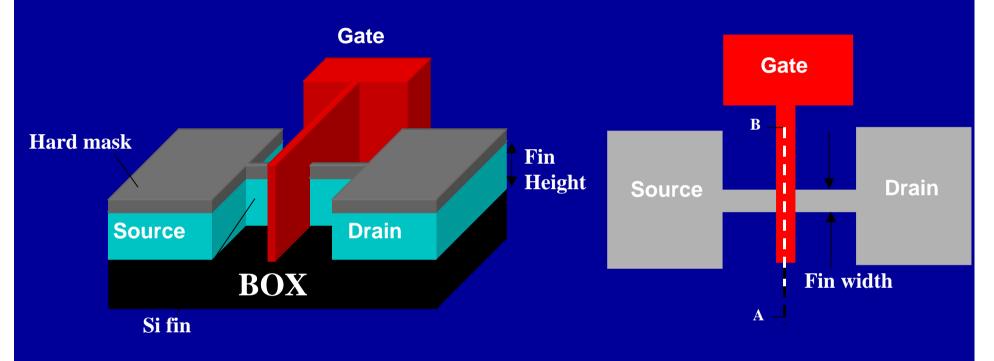

# **Quasi-planar SOI FinFET**

#### Advantages

- Relaxed constraint on channel thickness

- Relaxed constraint on EOT

- Improved SCE control

- Compatible with modern manufacturing steps

#### Issues

- Formation and control of fine Si fins

- Formation and control of sidewall spacer

- Parasitic S/D resistance

- Vth adjustment

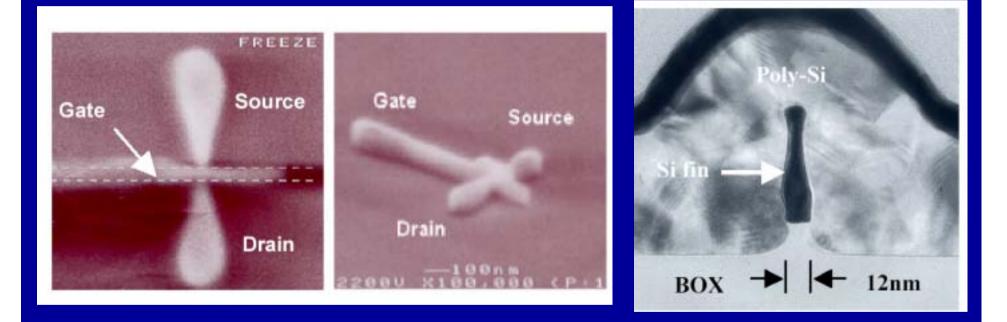

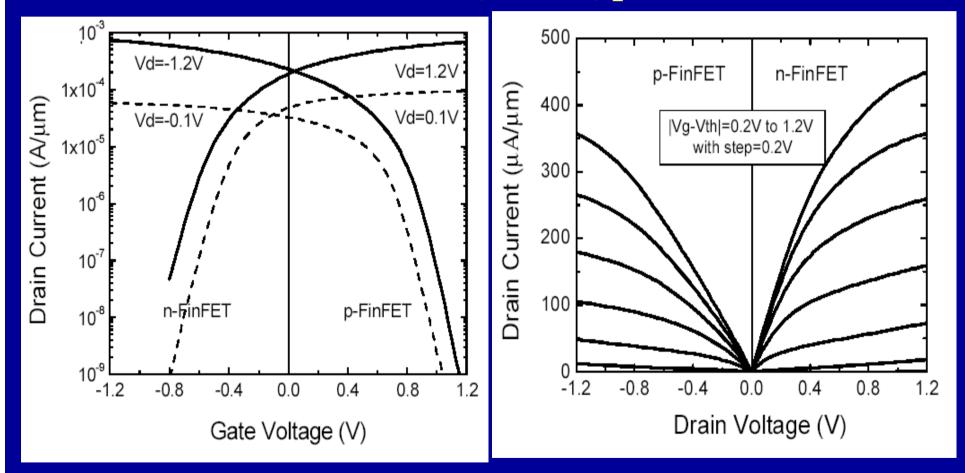

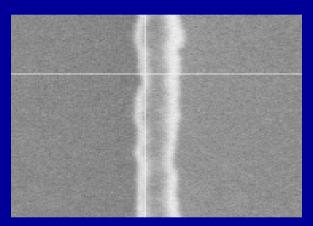

## 10 nm Gate Length FinFET (IEDM'2002, S.10.2, p.251)

## 10 nm Gate Length FinFET (IEDM'2002, S.10.2, p.251)

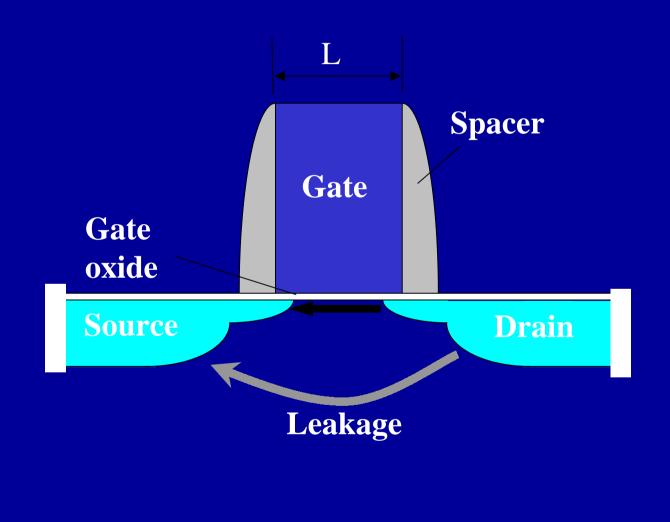

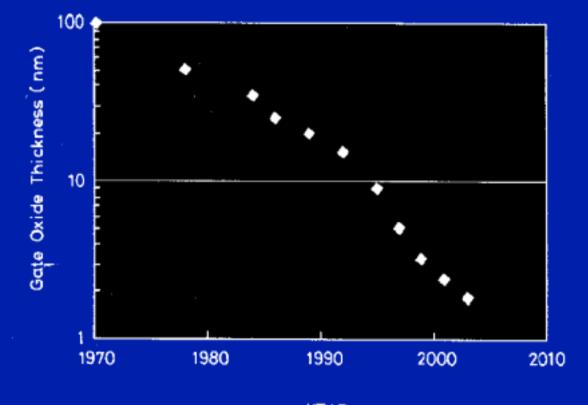

## **Major Issues for Device Scaling**

#### Leakage Currents

- Tunneling currents from gate to channel,

- body to drain, and source to drain

- Thermally generated subthreshold channel current

### • Fluctuation effects

- Line edge roughness

- Film thickness control ( channel and gate dielectric )

- Dopant distribution

- Power Consumption

### **MOSFET EFFECTIVE DIELECTRIC THICKNESS**

YEAR

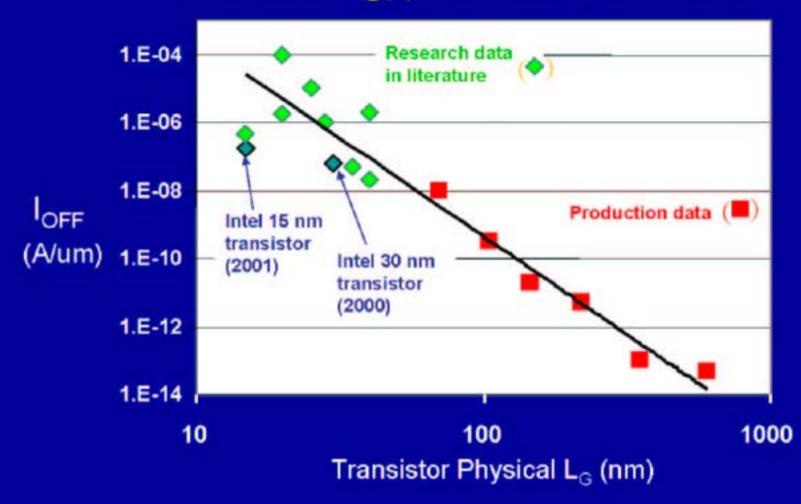

## Transistor I<sub>OFF</sub> Leakage Trend

## **Fluctuation Effects**

#### Line width

## **Film Thickness**

#### **Dopant concentration**

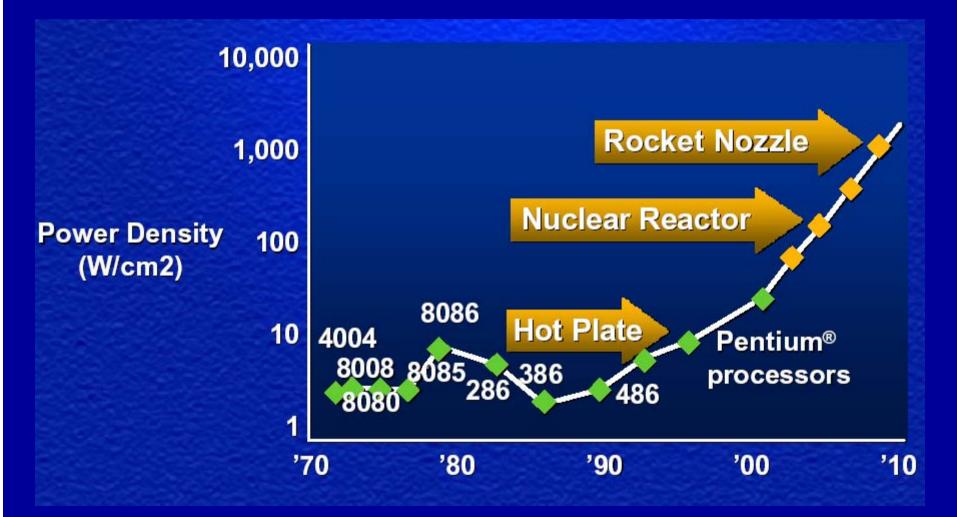

### **Power Density Will Get Even Worse** (Andrew S. Grove, Luncheon Talk in IEDM'02)

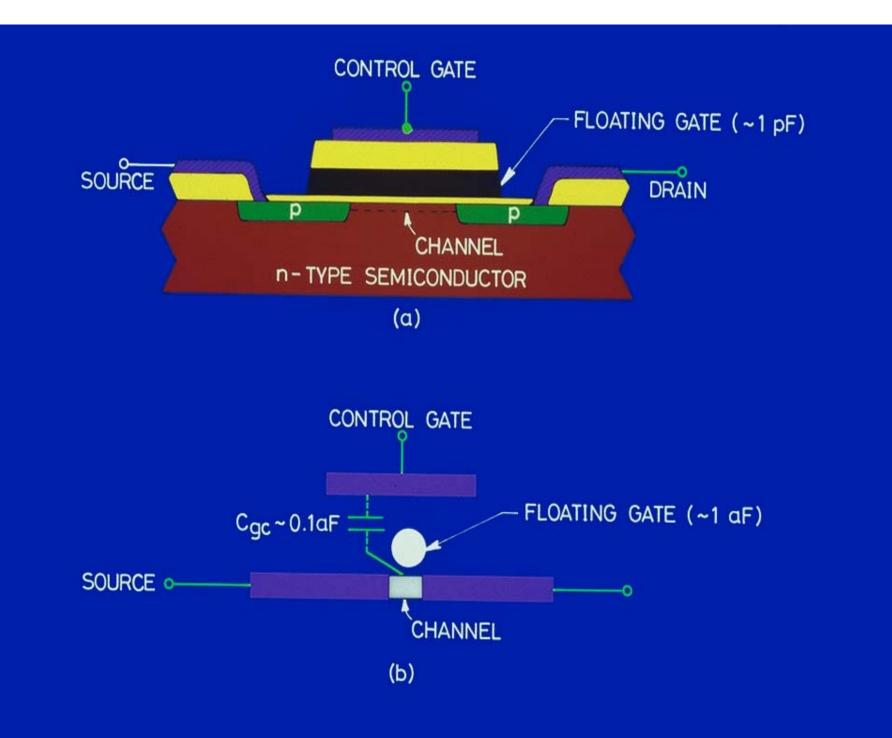

## **Nanoelectronic Devices Options**

#### **Molecular Devices**

Single electron transistor (SET)

#### Which can replace Si CMOS?

#### Spintronics

**Targets:** Lower cost Less power consumption Higher performance

## **Requirements for Nanotechnology Options**

- Feature size < 10 nm

- High energy conversion efficiency

- High speed

- Room temperature operation

- Good stability, uniformity and reliability

#### NANOTECHNOLOGY OPTIONS

#### Carbon-nanotube FET

- difficulty of forming low resistance contact

- difficulty in forming nanotubes with the desired physical features

- how to position nanotubes in a given position in a cost-effective way

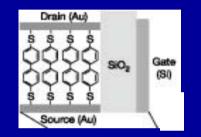

#### Molecular Devices

- limitation in operating temperature

- difficulty in making contact to individual molecules

#### Quantum-dot Cellular Automata (Single-electron Parametron)

- limitation in operating temperatures

- sensitivity to random background charge

- slow speed

- difficulty in transmitting signals across larger intra-die distances

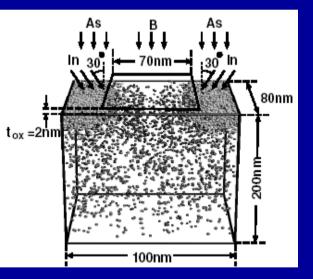

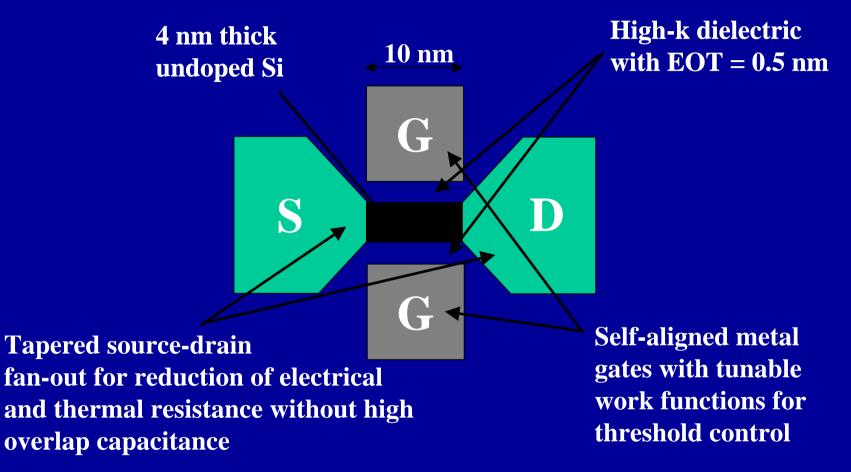

## **The Ultimate MOS Transistor**

(Y. Taur, in short course program of IEDM'01)

(ITRS'2001, 2016, 25 nm-node, physical gate length for MPU: 9 nm)

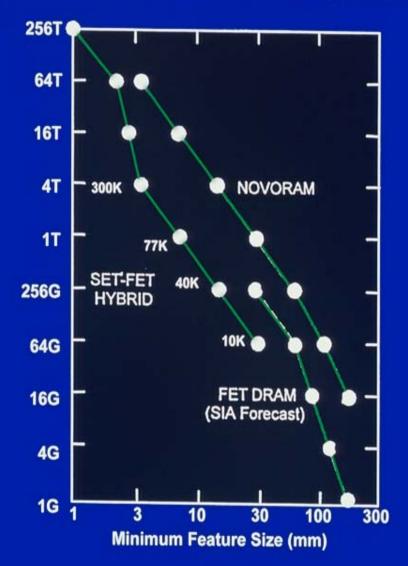

### **MEMORY DENSITY OF DRAM AND SET**

### **APPLICATIONS AT THE SCALING LIMIT**

| Application                                            | Memory   | Comp.<br>Rate   | Power / DSP     | Si Area |

|--------------------------------------------------------|----------|-----------------|-----------------|---------|

|                                                        | (GB)     | (GIPS)          | (VV)            | (cm²)   |

| Speech recognition ( to text)                          | 0.01-0.1 | 0.1-1           | 0.001           | 0.1     |

| Real time language translation                         | 0.1      | 1-10            | 0.01            | 0.2     |

| Video encoding, very high res.<br>(1920 ×1200, 30 fps) | 0.01     | 20-200          | 0.2             | 0.6     |

| 2-way video wrist watch                                | 0.01     | 0.05            | 0.0002          | 0.01    |

| PDA                                                    | 0.1      | 1-10            | 0.01            | 0.2     |

| Factoring 512 bit numbers                              | 1        | 4000            | 10              | 40      |

| Deep Blue chess                                        | 3        | 10000           | 3               | 100     |

| QM -based device simulation⁺                           | 10       | 100             | 30              | 15      |

| PetaFLOPS computing challenges*                        | 3×10⁴    | 10 <sup>6</sup> | 10 <sup>6</sup> | 5×10⁴   |

<sup>+</sup> Power based on general-purpose processor applications instead of DSP

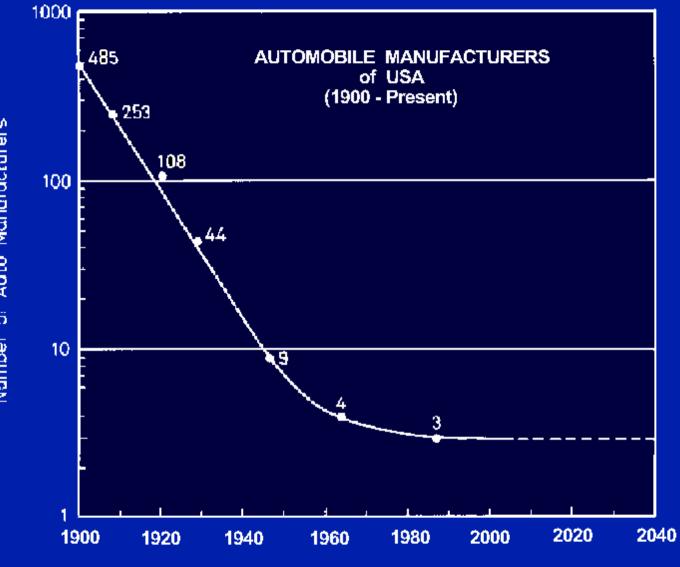

Number of Auto Manufacturers

YEAR

## CONCLUSION

- Major issues for device scaling are leakage currents, fluctuation effects, and power consumption

- The double-gate SOI MOSFET is a promising candidate for the ultimate device structure, its gate length can be scaled down to 10 nm

- There are numerous applications of MOSFET at the scaling limit ( around 2015 ), and silicon technology is expected to continue as the most powerful driver of the Information Age